Ja en els anys vuitanta, el pioner de la computació paral·lela Gene Amdahl va obrir un pla per accelerar la computació del mainframe: un processador de mida de wafer de silici. La informàtica seria més ràpida i més eficient, si fos possible mantenir la major part de les dades en el propi processador en lloc de fer-les circular a través d'una placa de circuit imprès cap a la memòria i altres xips, .

Amb 230 M US$ de capital risc, Amdahl va fundar Trilogy Systems per fer realitat aquesta visió. Un primer intent comercial de "integració a escala de wafer" va ser un fracàs. Els enginyers de la Universitat d'Illinois Urbana-Champaign i de la Universitat de Califòrnia Los Angeles, creuen que cal tornar a intentar-ho.

|

| Font: iStockphoto |

En el Simposi Internacional de l' IEEE sobre Arquitectura de Computadors d'Alt rendiment en el Febrer del 2019, el professor associat d'enginyeria informàtica d'Illinois, Rakesh Kumar i els seus col·laboradors, van presentar el cas d'una computadora a escala de wafer, que comprenia fins a 40 GPU. Les simulacions d'aquest 'monstre' de multiprocessador van accelerar els càlculs gairebé 19 vegades i van reduir la combinació del consum d'energia i el retard del senyal més de 140 vegades.

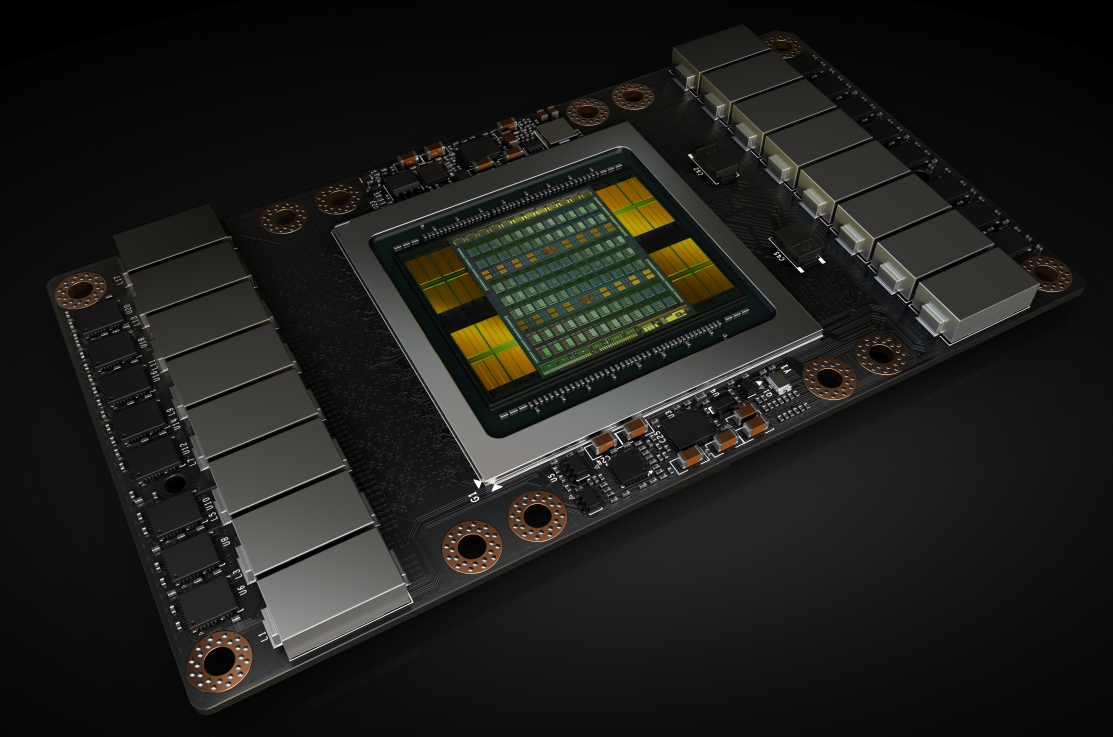

"El gran problema que estem tractant de resoldre és la sobrecàrrega de comunicació entre unitats computacionals", explica Kumar. Els supercomputadors propaguen rutinàriament aplicacions a través de centenars de Graphic Processing Unit (GPU) que viuen en circuits impresos separats i es comuniquen a través d'enllaços de dades. Aquests enllaços, absorbeixen energia i són lents en comparació amb les interconnexions. A més, a causa de la incompatibilitat entre les propietats mecàniques dels xips i les plaques de circuit imprès, els processadors s'han de mantenir en paquets que limiten el nombre d'entrades i sortides que un xip pot utilitzar. Per tant, obtenir dades d'una GPU a una altra implica una quantitat increïble de despeses generals.

El que es necessita són les connexions entre mòduls GPU que són ràpides, de baix consum i abundants, tant com les interconnexions en els xips. Aquestes connexions ràpides integrarían aquestes 40 GPU fins al punt que actuarien com una gegant GPU. Des de la perspectiva del programador, tot és el mateix GPU.

|

| https://devblogs.nvidia.com/wp-content/uploads/2017/05/SXM2-VoltaChipDetails.png |

Una solució seria utilitzar tècniques estàndard de fabricació de xips per construir les 40 GPU en el mateix waffer de silici i afegir interconnexions entre elles. Però aquesta és la filosofia que va fallar l'intent d'Amdahl als anys vuitanta. Sempre hi ha la possibilitat d'un defecte quan es fa un xip, i la probabilitat que hi hagi un defecte augmenta amb la mida del xip. Si un xip és de la mida d'un plat del sopa, gairebé està garantit que sorgeixi un error en algun lloc.

Per tant, té més sentit començar amb xips GPU de mida normal que ja han superat proves de qualitat i disposen d'una tecnologia per connectar-los millor. L'equip creu que ho tenen en una tecnologia anomenada tela d'interconnexió de silici ( SiIF ). SiIF reemplaça la placa de circuit amb silici, de manera que no hi ha una incompetència mecànica entre el xip i la base.

El waffer de SiIF, està modelat amb una o més capes d'interconnexions de coure de 2 micres d'ample, separades entre si en 4 micròmetres. Això és comparable al nivell superior d'interconnexions en un xip. En els llocs on les GPU estan destinades a connectar-se, el waffer de silici està modelat amb curts pins de coure, separats unes 5 micres de distància. La GPU està alineada per sobre d'aquestes. Aquest procés, es connegut com l'enllaç de compressió tèrmica elqual, fa que els pins de coure es fusionin amb les interconnexions de coure de la GPU. La combinació d'interconnexions estretes i d'espaiat ajustat, significa que pot comprimir almenys 25 vegades més, segons els investigadors d'Illinois i UCLA.

|

| https://www.cgdirector.com/wp-content/uploads/media/2017/03/nvidia-geforce-rtx-2080ti-2080-2070-series-gpu.jpg |

Kumar i els seus col·laboradors van haver de tenir en compte una sèrie de restriccions en el disseny de la GPU a escala de wafer, incloent la quantitat de calor que es podia disipar del waffer, com la distribució d calor de manera que les GPU podien comunicar-se amb més rapidesa.

La potencia, va resultar ser una de les limitacions més restrictives. En aplicar la tensió estàdard d'un volt en el xip, el cablejat del waffer de SiIF consumirà 2 quilowatts. En lloc d'això, l'equip de Kumar va augmentar la tensió a 48 volts, reduint la quantitat de corrent necessària i, per tant, les pèrdues de potencia. Aquesta solució necessitava disposar reguladors de tensió i condensadors de senyals al voltant del waffer, ocupant espai que podria haver estat més mòduls de GPU.

Encara que, en un sol disseny es van poder comprimir en 41 GPUm, es van provar una simulació d'aquest disseny i es va trobar que va accelerar tant la computació com el trànsit de dades mentre consumia menys energia que els 40 servidors GPU estàndard que feien falta.

Font: IEEE spectrum

Cap comentari:

Publica un comentari a l'entrada